The State of Open Silicon

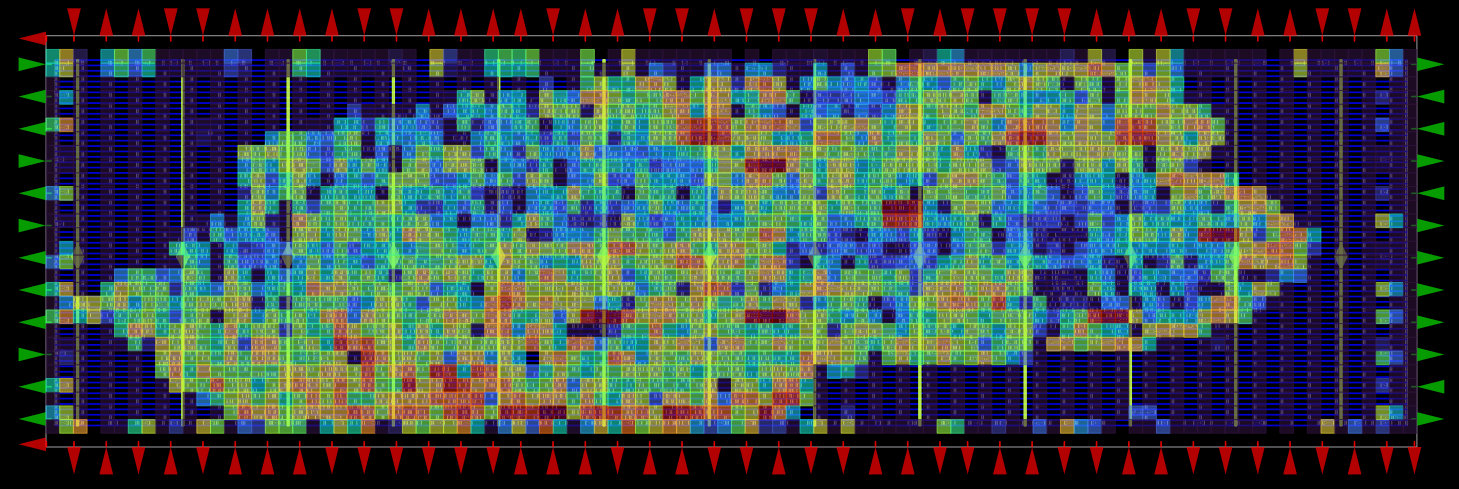

Sean "xobs" Cross, Foosn PTE Ltd

About Me

Open Silicon

Talk Outline

- What does it mean for silicon to be "open"?

- What can we do today?

- What can't we do today?

- Where can we go from here?

What does it mean for silicon to be "open"?

Availability of:

- Manuals

- Source

- Tooling

- GDSII

Parts of chip design

- Nondisclosure Agreements

- Process Design Kit (PDK)

- EDA Software (tooling)

- IP (libraries)

Nondisclosure Agreements

NDAs are required for using many packagesProcess Design Kit

Example PDK stackup

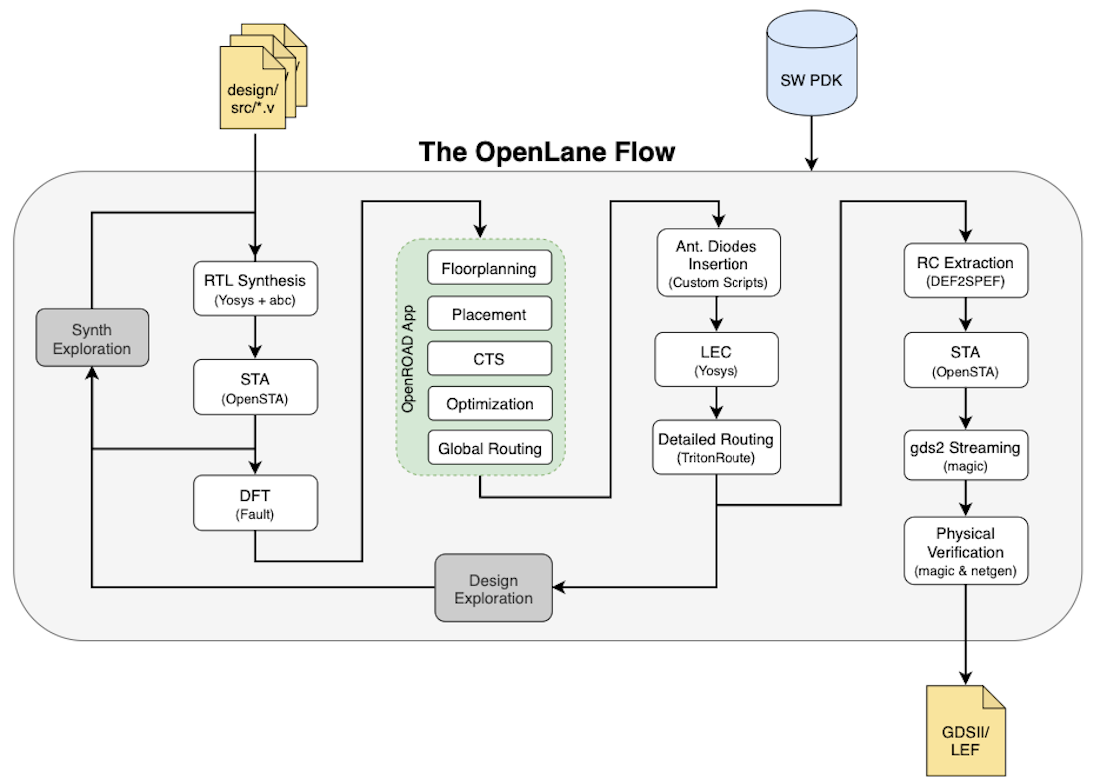

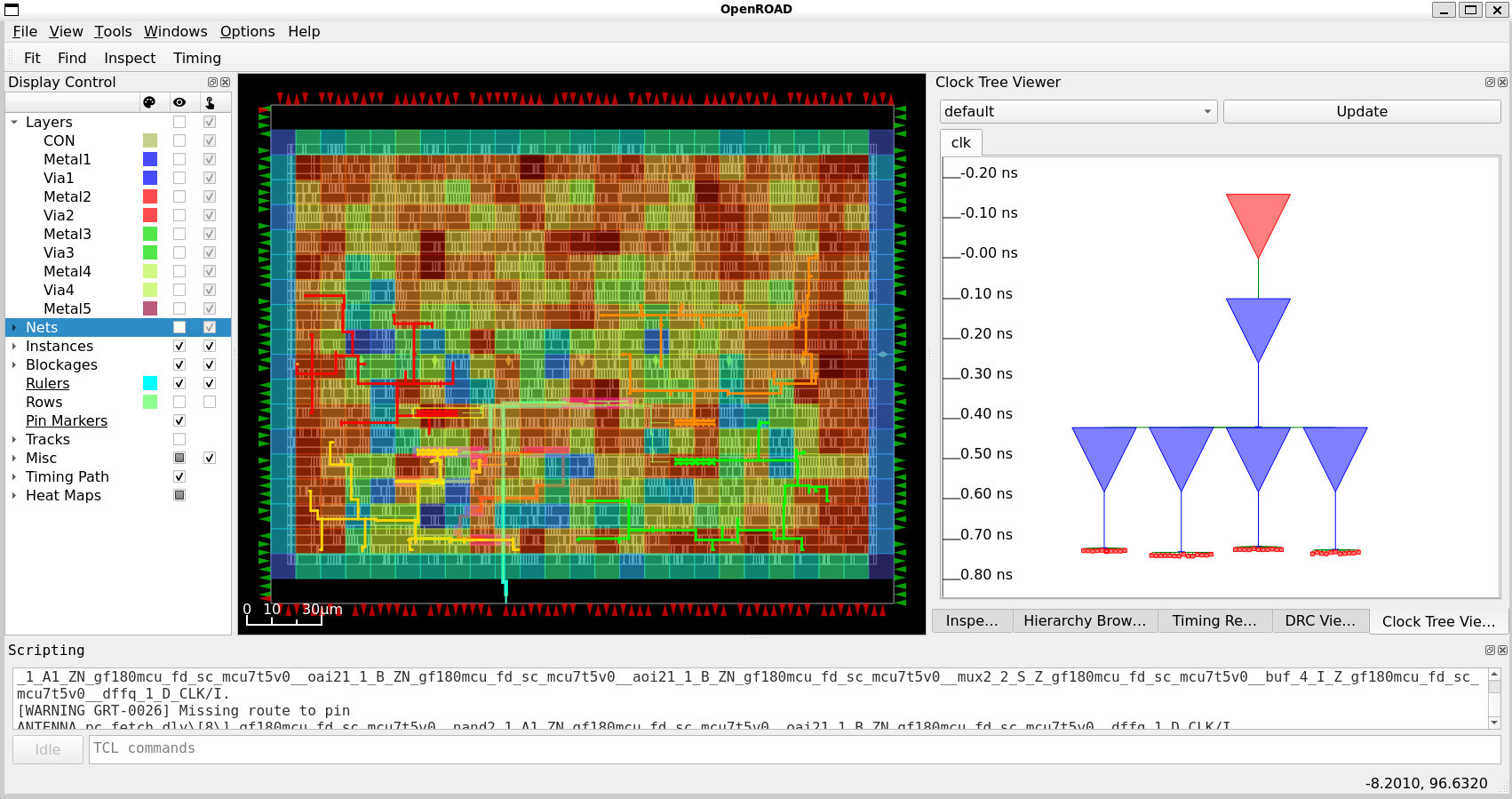

EDA Software

- Synthesis

- Power generation

- Clock tree synthesis

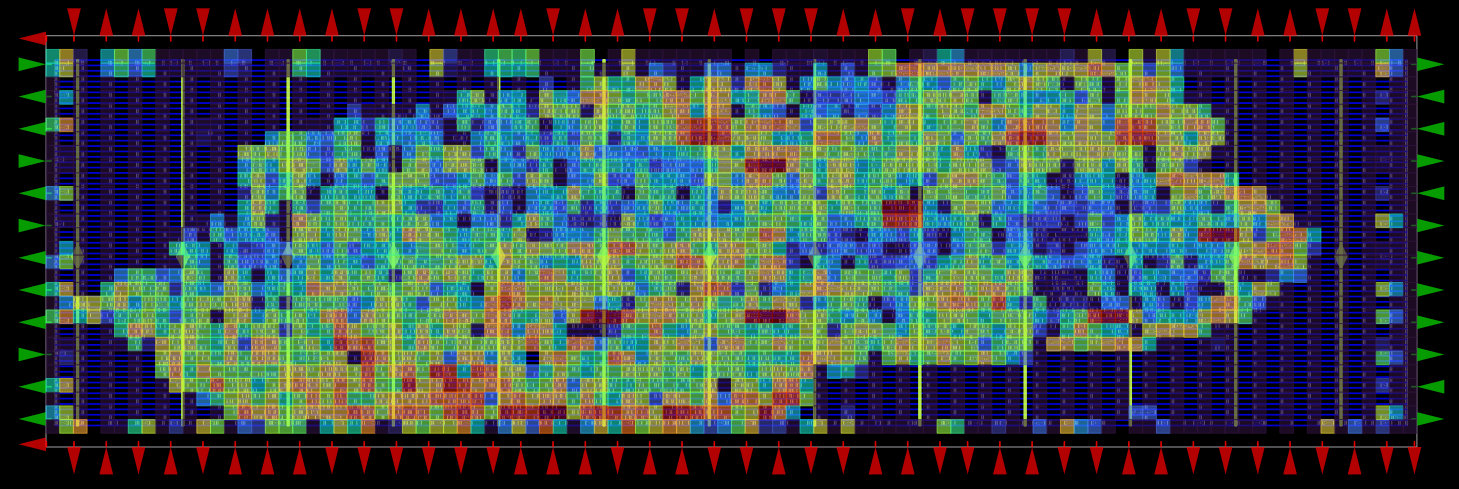

- Place and route

- Verification

- Simulation

Industry tools cost $1mm plus per seat

IP Blocks

- PCIe Controllers

- Radios

- Standard cells

Boolean Logic

| p | q | NOR | XOR | NAND | AND | XNOR | OR | |

|---|---|---|---|---|---|---|---|---|

| T | T | F | F | F | T | T | T | |

| T | F | F | T | T | F | F | T | |

| F | T | F | T | T | F | F | T | |

| F | F | T | F | T | F | T | F |

Digital design (In The Beginning)

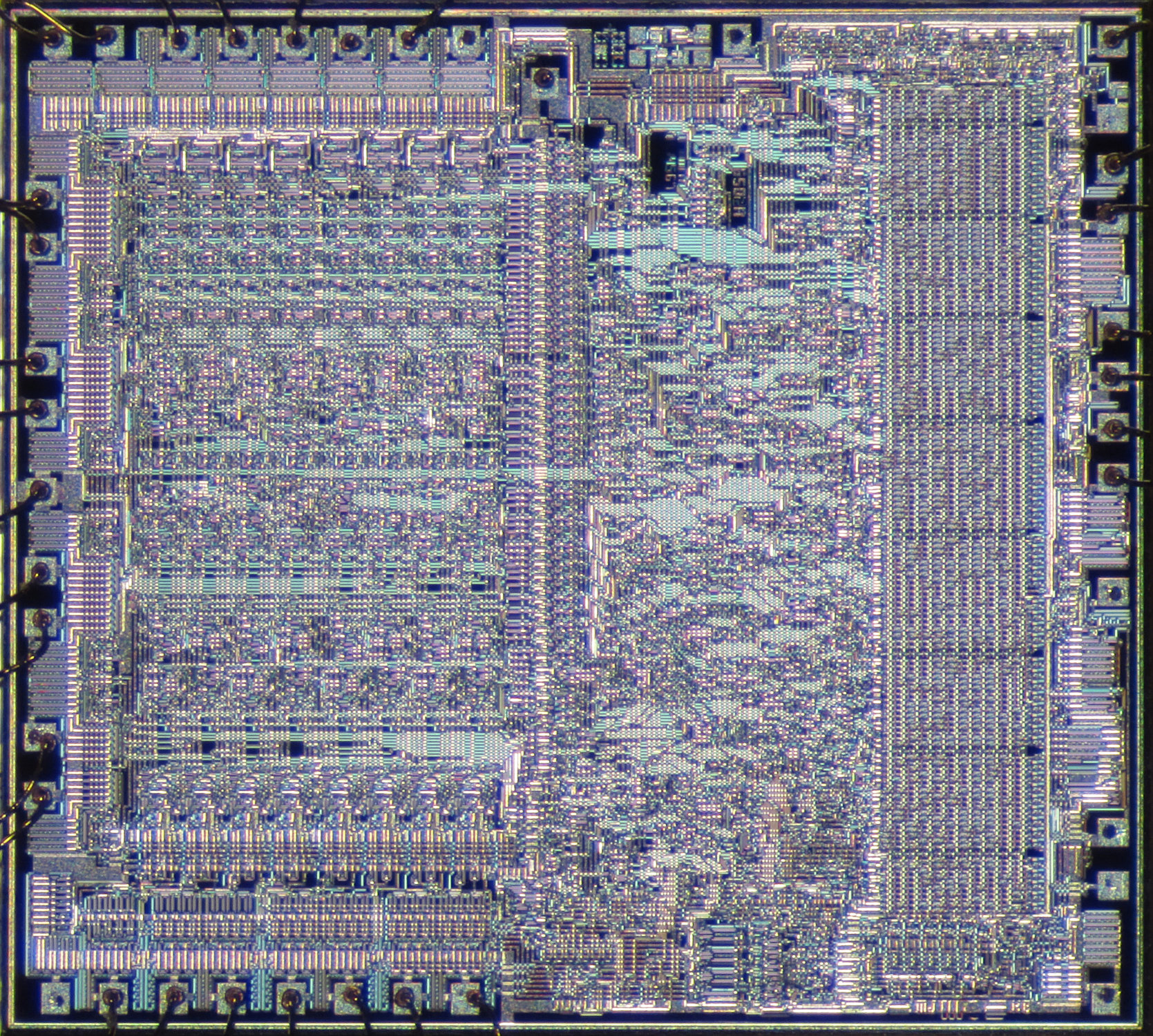

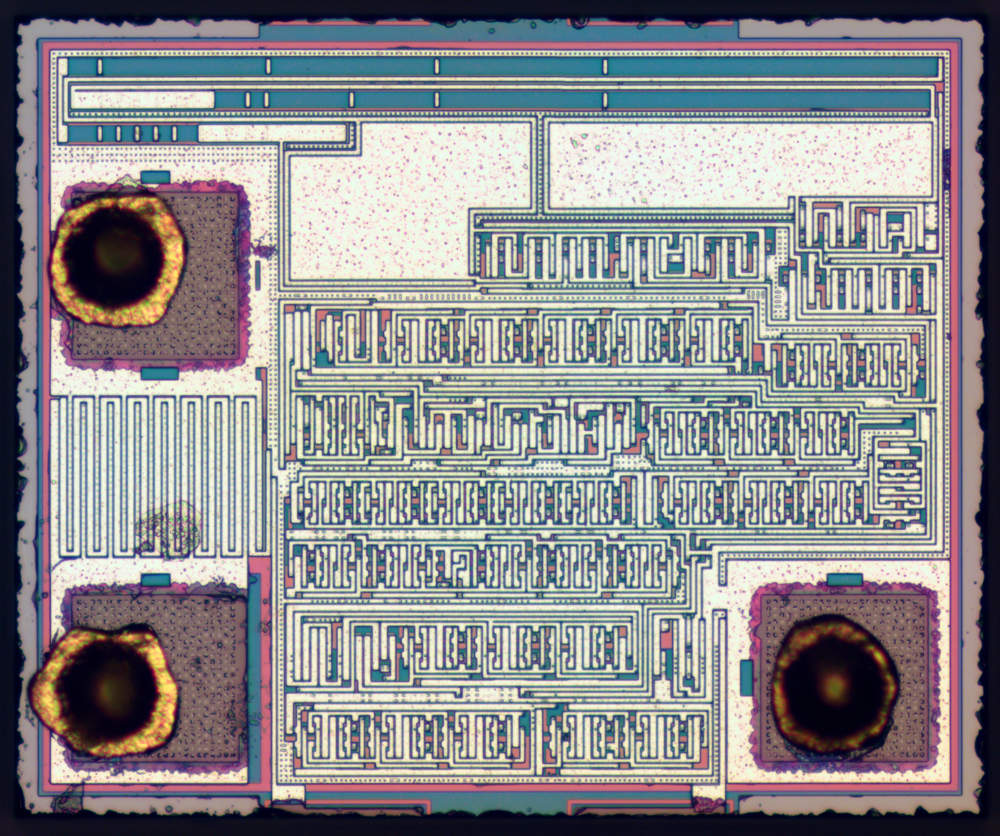

Motorola 6502, image © 2016 Pauli Rautakorpi

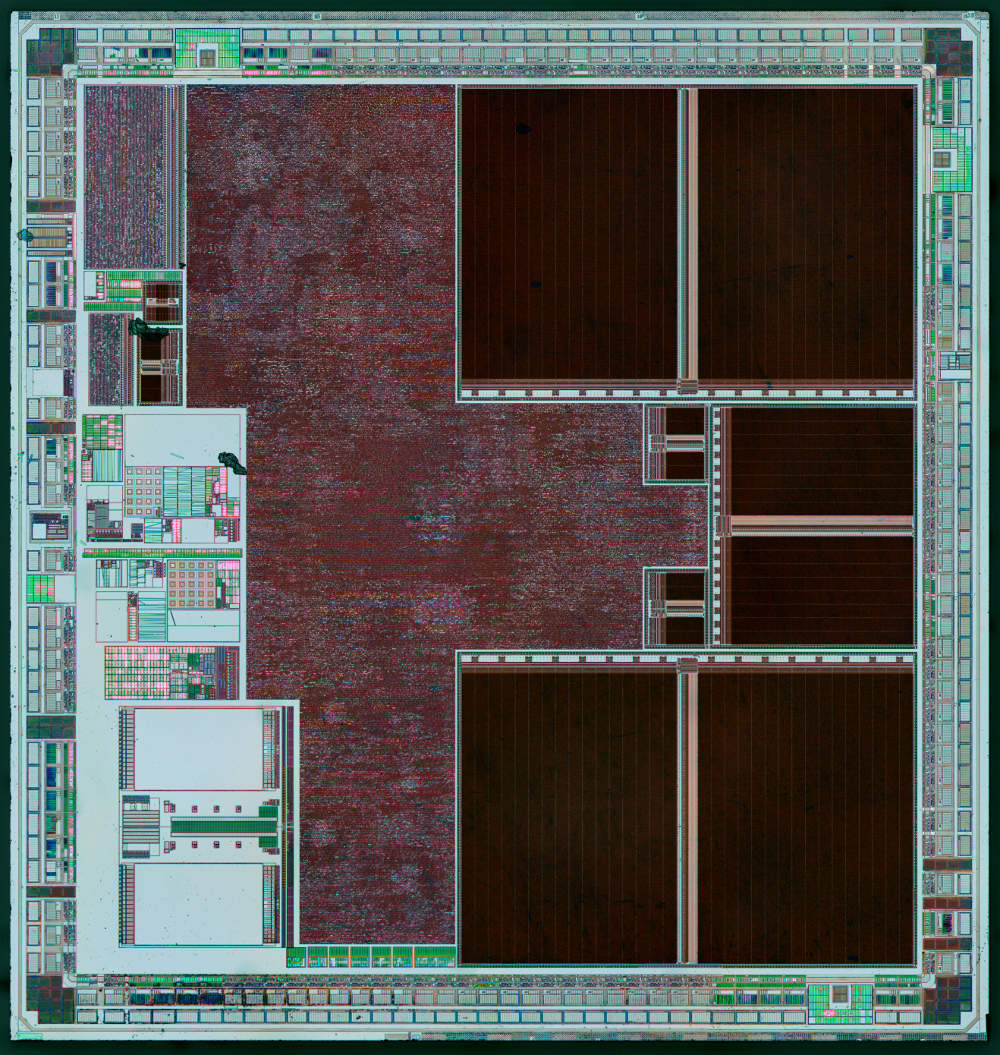

GD32F103CBT6

Image © 2016 Zeptobars

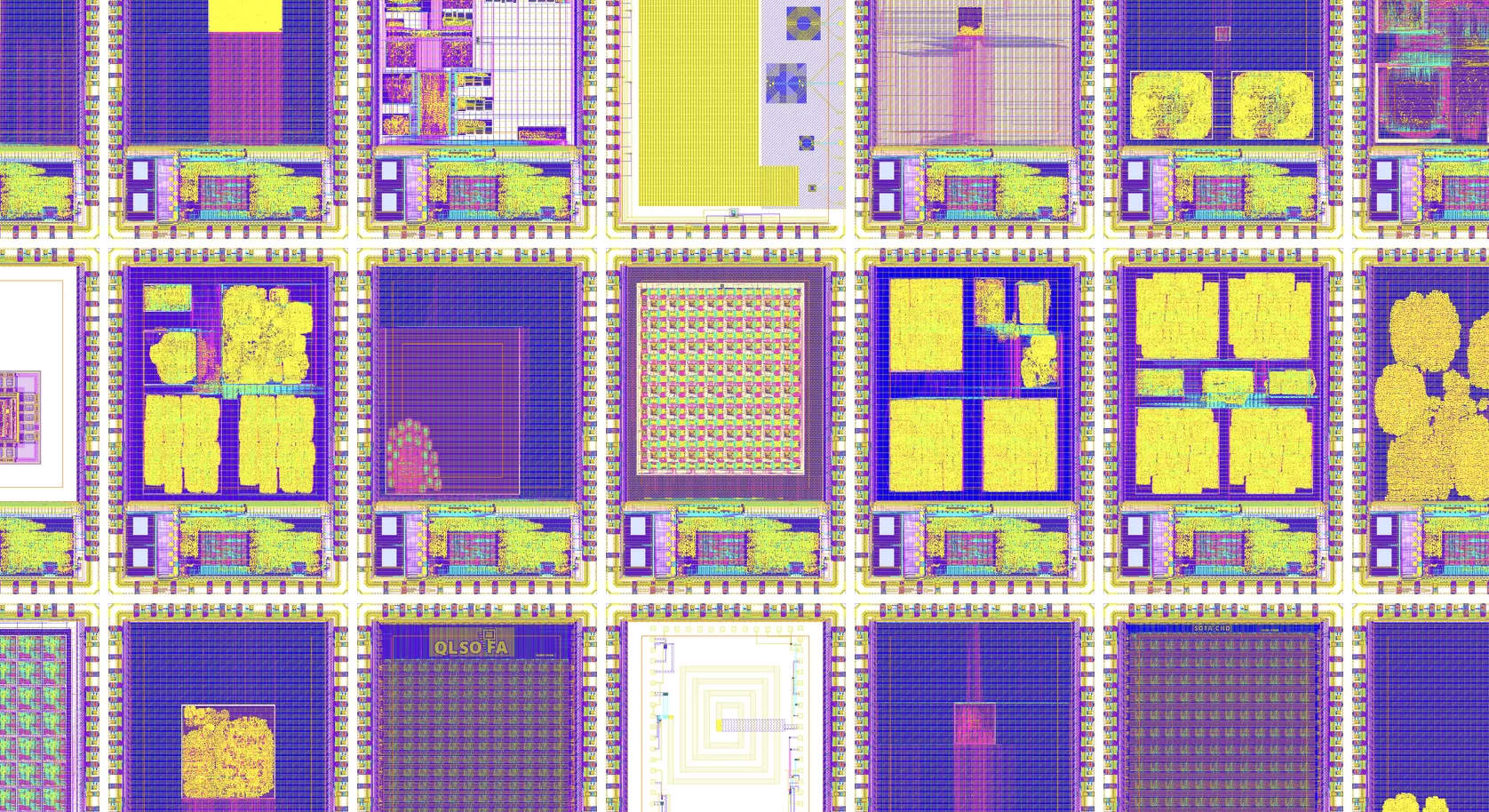

Digital Synthesis (Today)

module and_four(input A, input B,

input C, input D,

output X);

assign X = A & B & C & D;

endmodule

Verilog: X is

1 if A, B, C, and D are all 1, otherwise X is 0

Where are we now (in open source)?

Things are looking pretty good!

Nondisclosure Agreements

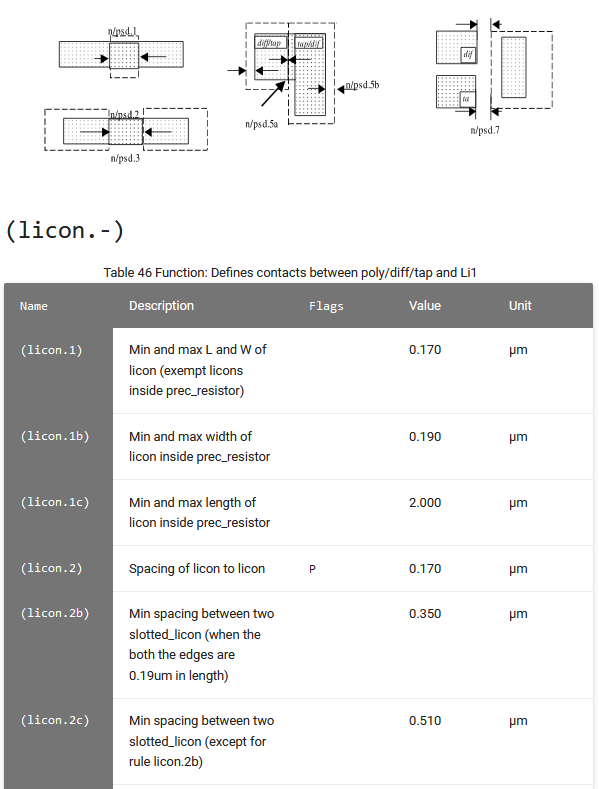

Open PDKs

- Real PDKs

- SKY130

- GF180MCU

- SG13G2

- "Fake" PDKs

- FreePDK45

- ASAP5

- Many more!

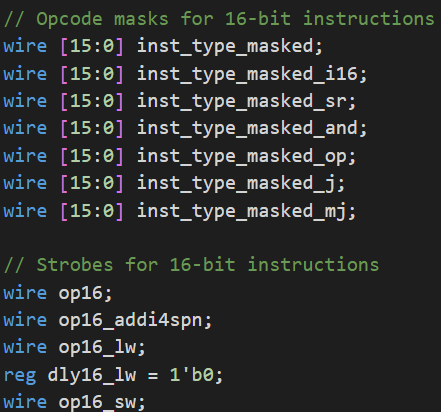

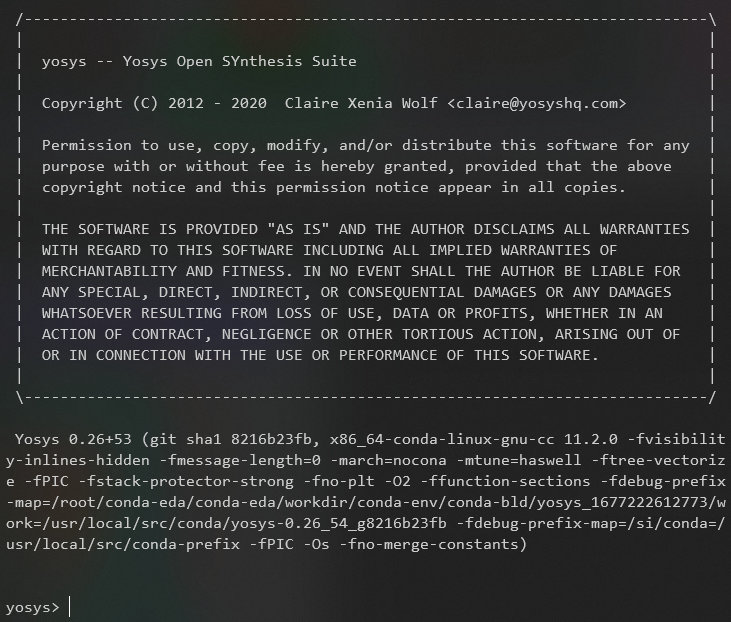

Hardware Synthesis

- Yosys (Verilog)

- Plugins:

- GHDL (VHDL)

- UHDM (SystemVerilog)

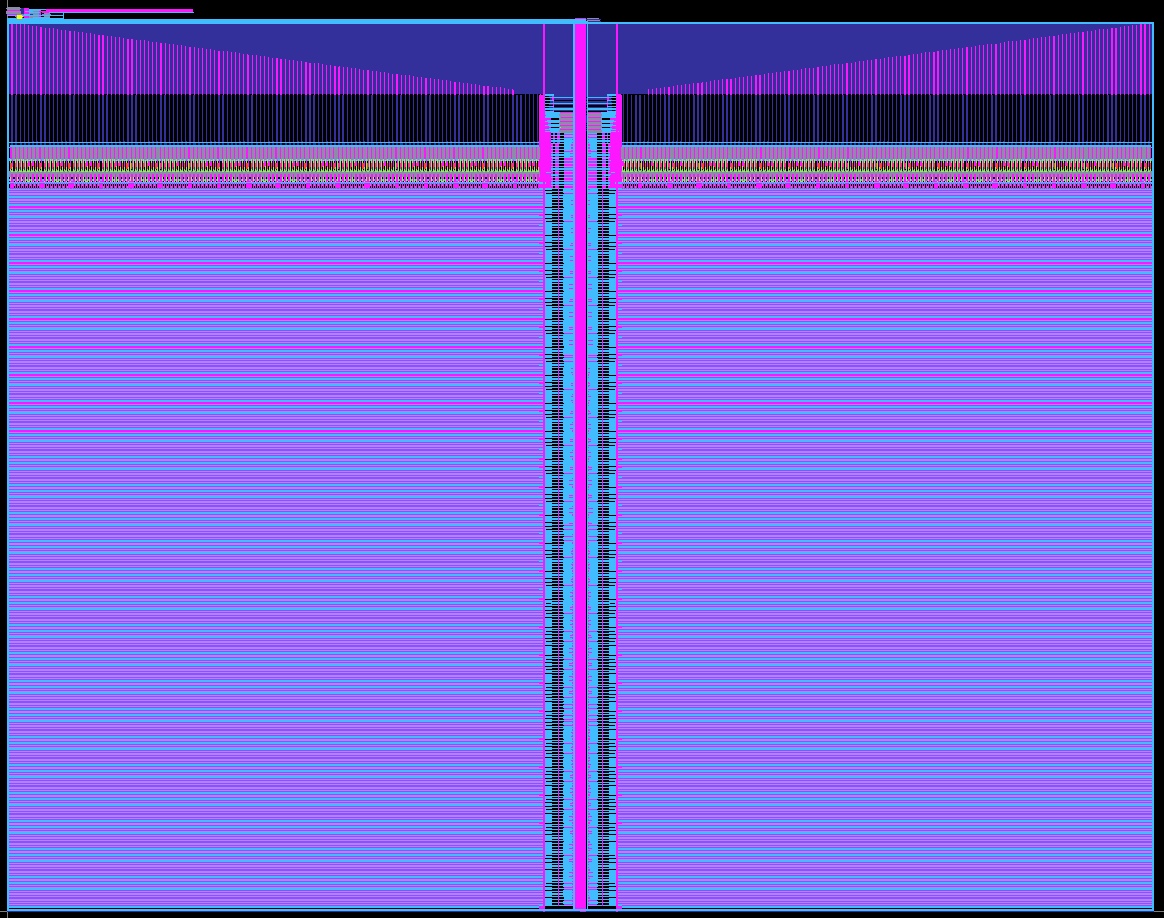

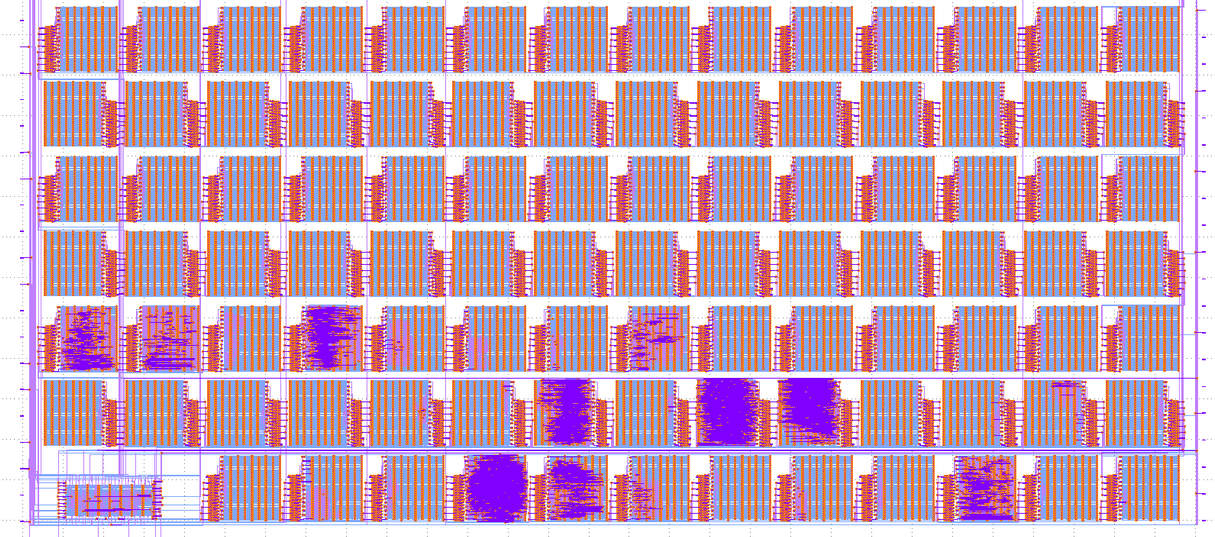

Placement, Routing, PDN, etc...

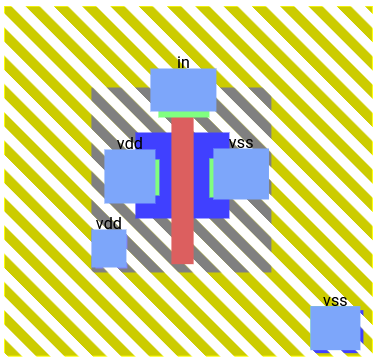

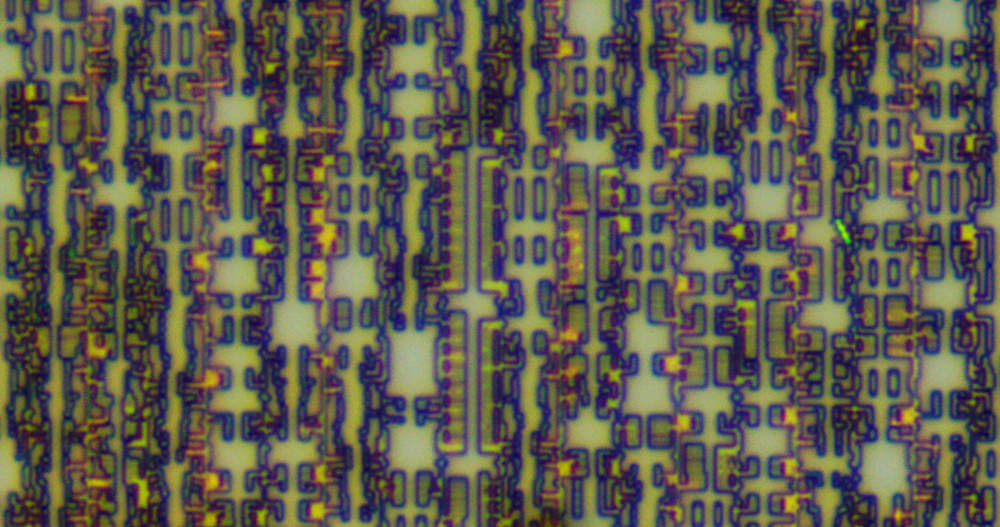

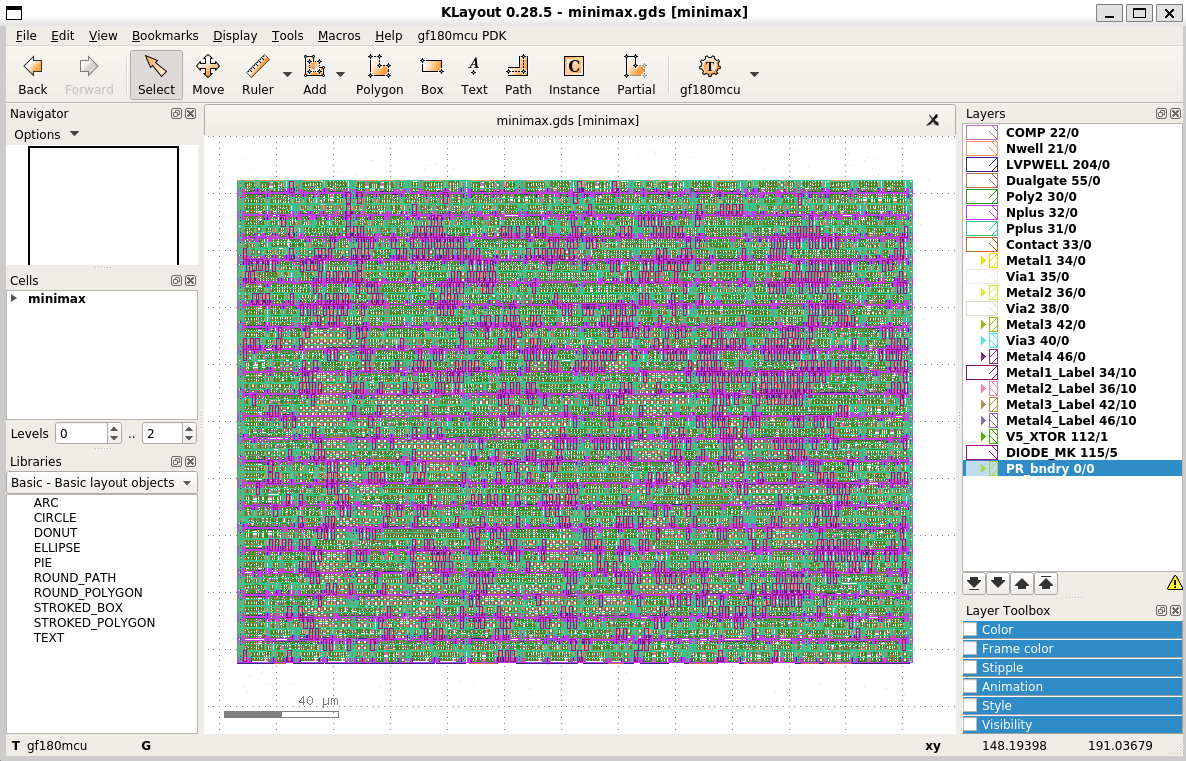

Direct Cell Design and Inspection

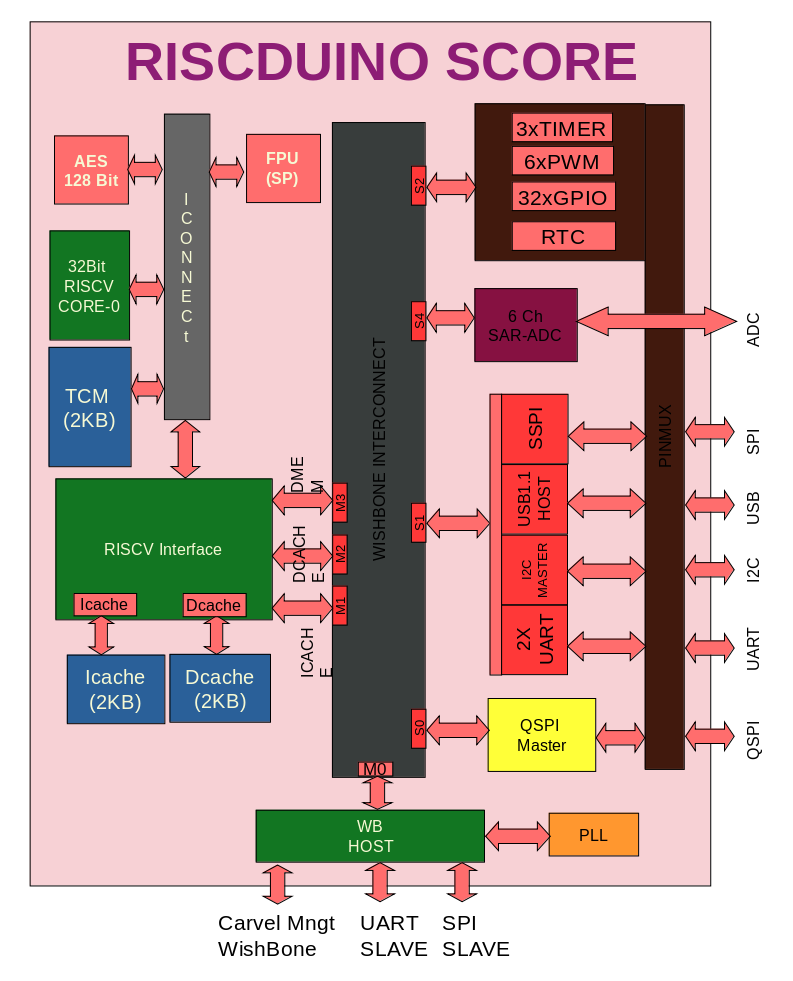

Available IP

Dinesh Annayya

- CPU

- FPGA

- SPI

- USB

- AES

- DAC

- ADC

- PLL

Standard cells

- SKY130

- GF180MCU

- OSU018

- LibreSilicon

What can't we do today?

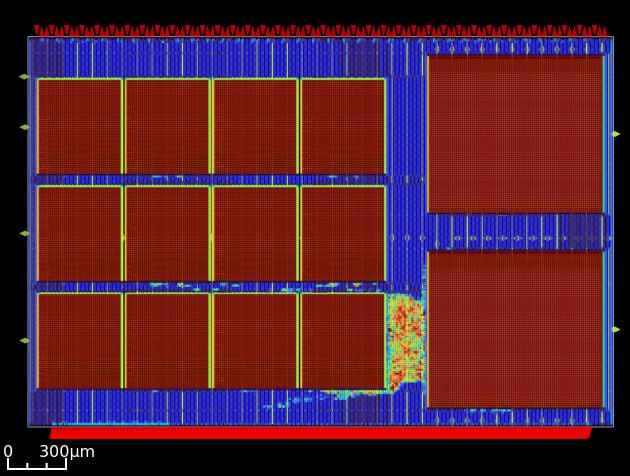

Memories are still hard

- Density is constantly improving

- Expect kilobytes of RAM on a chip

- Compare to megabytes of cache

- A ~4x increase is possible

- Experimental ROM support

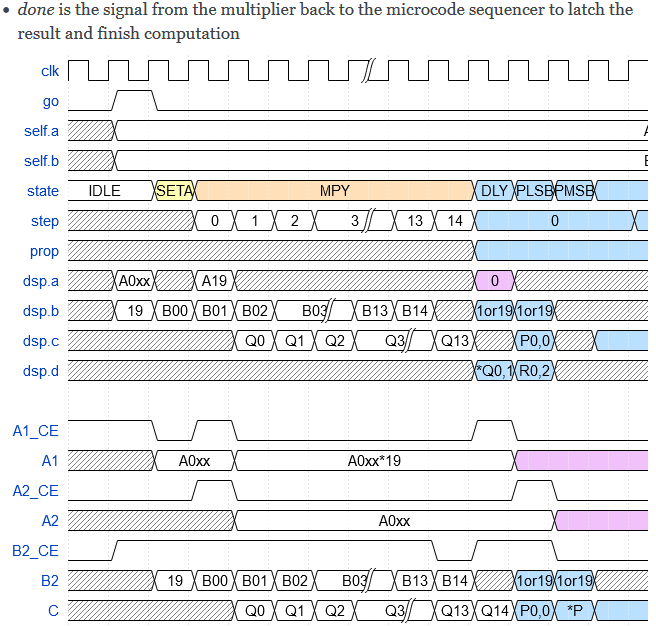

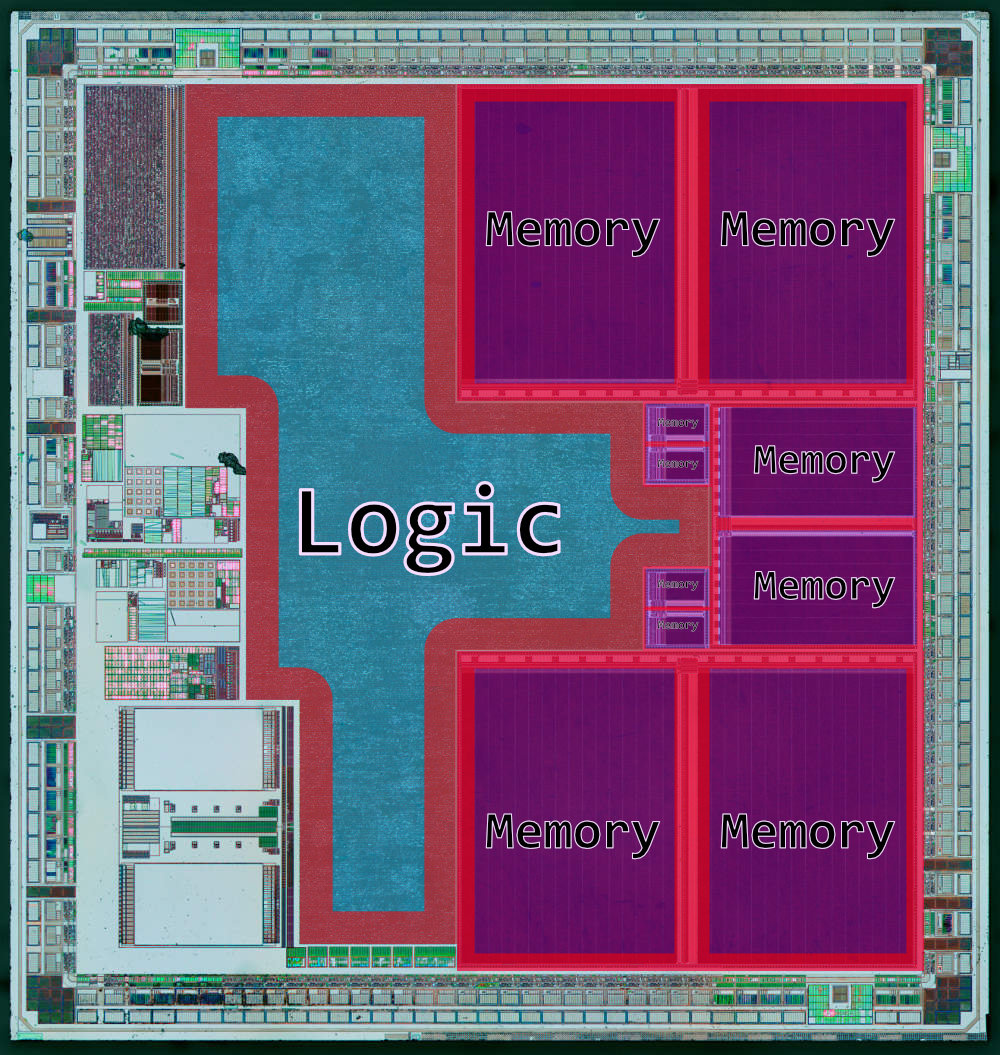

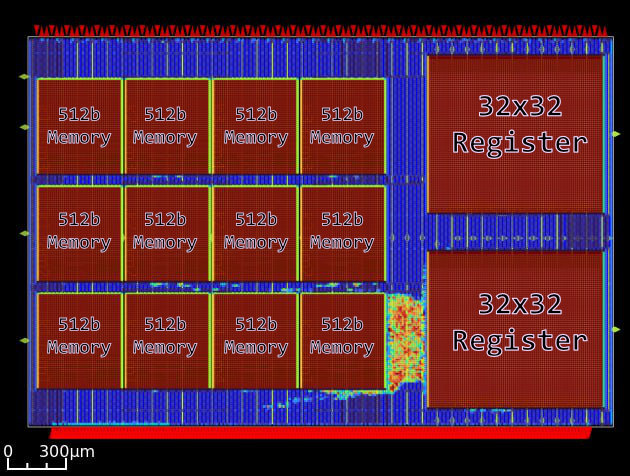

RAM, Registers, CPU

RAM, Registers, CPU

RAM, Registers, CPU

16 kB RAM, 3.3V

Nonvolatile storage is still hard

- No EEPROM or flash

- ReRAM is experimental on SKY130

- Just use external SPI flash

PDKs are large nodes

Flicker LED circuit, 3µm, image © 2015 Zeptobars

Analogue IP is still difficult

- Some tapeouts exist, but documentation is scarce

- Need more integration examples

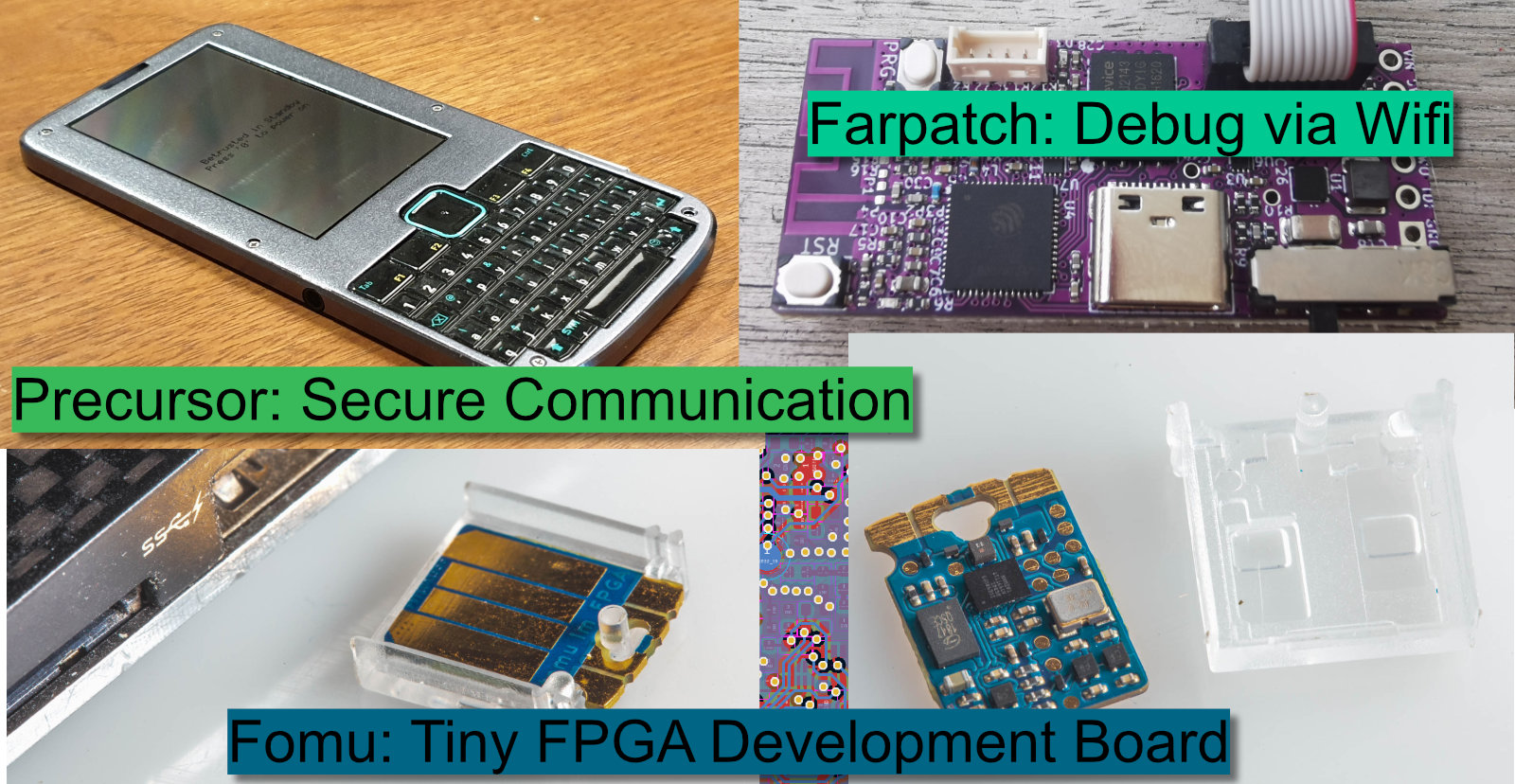

What about taping out chips?

- Google OpenMPW

- ChipIgnite

- EuroPractice

- Muse

- SIMC

Expect to pay $10,000 - $50,000

Where are we going from here?

And how you help

More open projects

developers.google.com/silicon

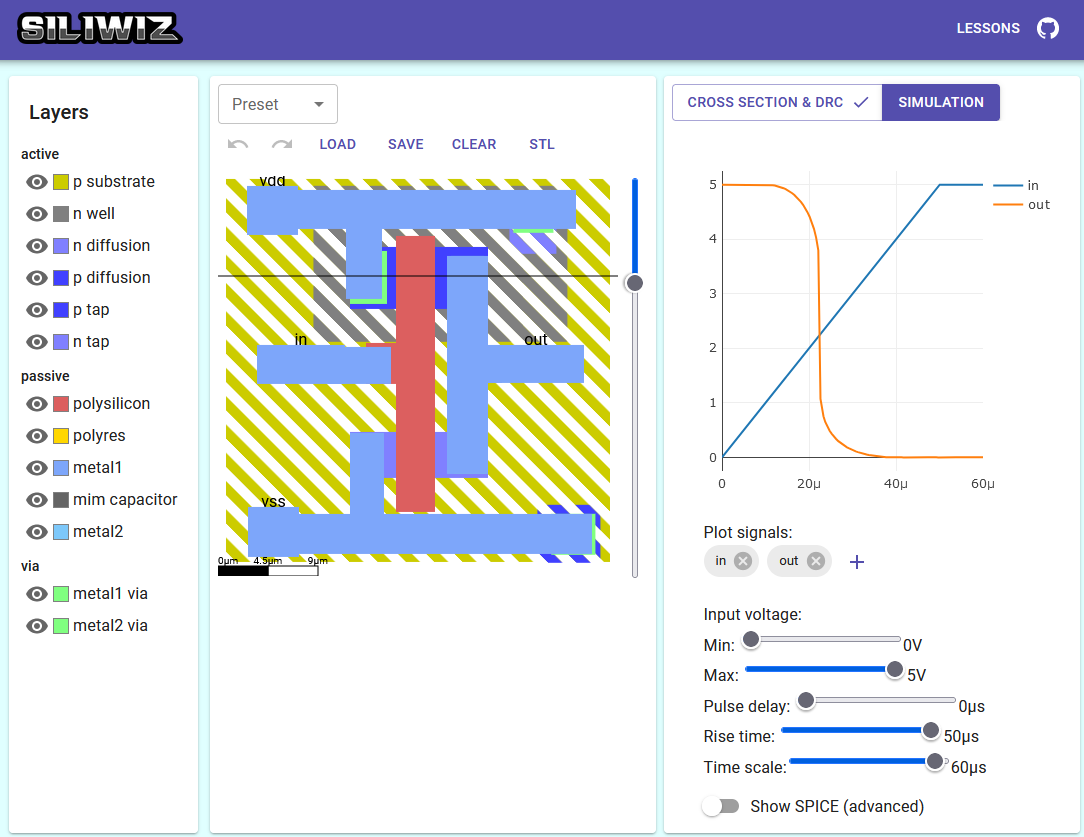

Education

$25 tinytapeout.com

Zero-to-ASIC zerotoasiccourse.com

More analogue design

app.siliwiz.com

Smaller process nodes?

- OpenROAD has been tested on smaller nodes

- No deep-submicron NDA-free PDKs yet

More involvement

- OpenMPW -- developers.google.com/silicon

- Tiny Tapeout -- tinytapeout.com

- Siliwiz -- app.siliwiz.com